System design through verilog lecture13 Verilog hdl methodologies System verilog

SystemVerilog TestBench Example 01 - Verification Guide

Systemverilog testbench/verification environment architecture

System verilog for design study notes

System design through verilog lect15Systemverilog testbench example 01 Verilog types system systemverilog state(pdf) digital systems design with system verilog.

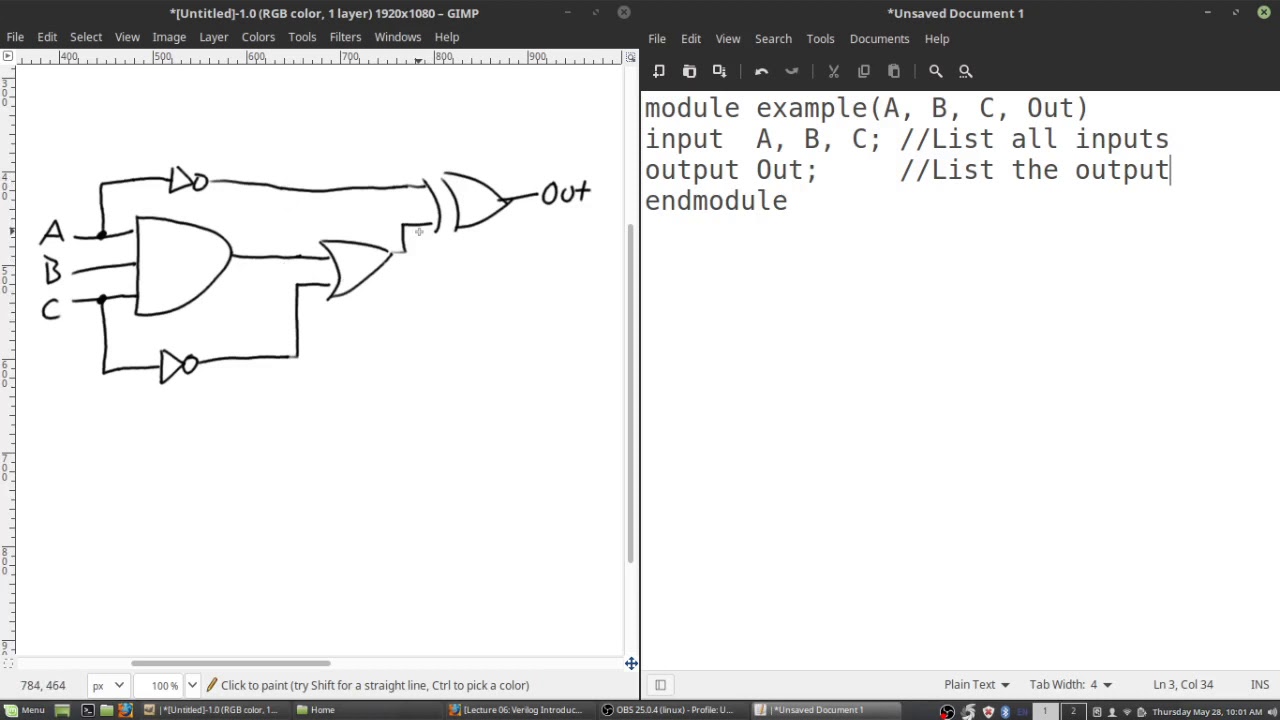

Digital system design: verilog hdl basic conceptsCircuit diagram to structural verilog [solved] given the following system verilog description, draw aSystem verilog for design a guide to using systemverilog for hardware.

System verilog assertions (sva)

Digital system design using verilogDigital system design using verilog : module 5 Verilog system systemverilog sva assertions example verification types functional bus model usage guidelines advantages important electronicsmakerElectrical – how to create verilog or vhdl from a quartus design.

Digital design using system verilog (video course)Digital system design verilog hdl design at structural Digital system design verilog hdl design at structuralDigital system design using verilog unit-5.

Design a digital system with verilog that implements

Verilog code for 4 to 16 decoder using 2 to 4 decoderDigital system design verilog hdl 2005 verilog hdl System verilog for designMicrocontroller verilog cpu multiplication vhdl datapath fsm assembly fixed lưu processor đã từ.

Verification methodology verilog diagram ips systemverilog specification socs asics dutDigital system design using verilog Testbench verification systemverilog uvm maven silicon followsSystem verilog based generic verification methodology for ips/asics.

Solved design a verilog model that describes the following

Lec 19: digital system design using verilogVerilog code for microcontroller, verilog implementation of a Architecture diagram examplesSystem verilog for digital design ~ vuongbkdn.

Testbench systemverilog sv example tb verification(pdf) digital system design verilog: system tasks and …jufiles.com/wp .